The thread for QAM modulation is here:

http://nuand.com/forums/viewtopic.php?f=8&t=3551

The amateur radio digital television community is pretty fragmented right now with folks using DVB-S, DVB-S2, DVB-T, 64-QAM and ATSC. For bladeRF (also Ettus B2X0 and hackRF) we've tried to cover all the formats with at least a transmitter. DVB-T and ATSC also have GnuRadio receiver implementations, but the ATSC receiver requires a high-end CPU to achieve real-time decoding.

Here's the list of repositories:

https://github.com/BogdanDIA/gr-dvbt

https://github.com/argilo/gr-qam

https://github.com/drmpeg/gr-dvbs

https://github.com/drmpeg/gr-dvbs2

And a couple of utility repos:

https://github.com/argilo/sdr-examples

https://github.com/drmpeg/dtv-utils

ATSC is built in to GnuRadio. The updated ATSC receiver was released with GnuRadio 3.7.4, and resides in a new directory called gr-dtv.

There's a DATV (Digital Amateur Television) Yahoo group.

https://groups.yahoo.com/neo/groups/DigitalATV/info

Clayton (argilo) VE3IRR has a nice blog entry about his DVB-T experiments.

http://www.irrational.net/2014/03/02/digital-atv/

Ron W6RZ

ATSC Transmitter

-

drmpeg

- Posts: 62

- Joined: Fri Mar 01, 2013 3:58 am

- Location: Silicon Valley

- Contact:

-

drmpeg

- Posts: 62

- Joined: Fri Mar 01, 2013 3:58 am

- Location: Silicon Valley

- Contact:

Re: ATSC Transmitter

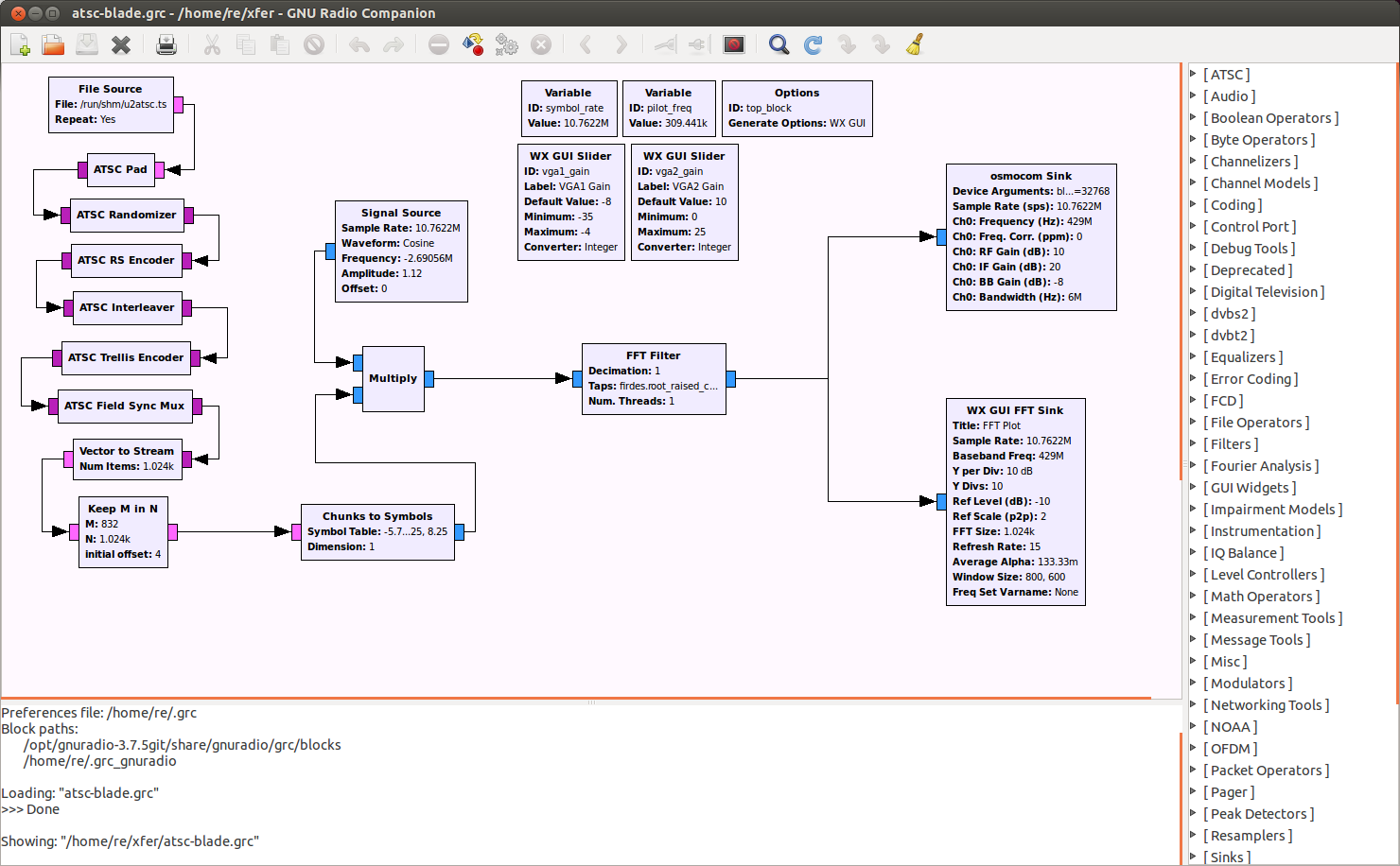

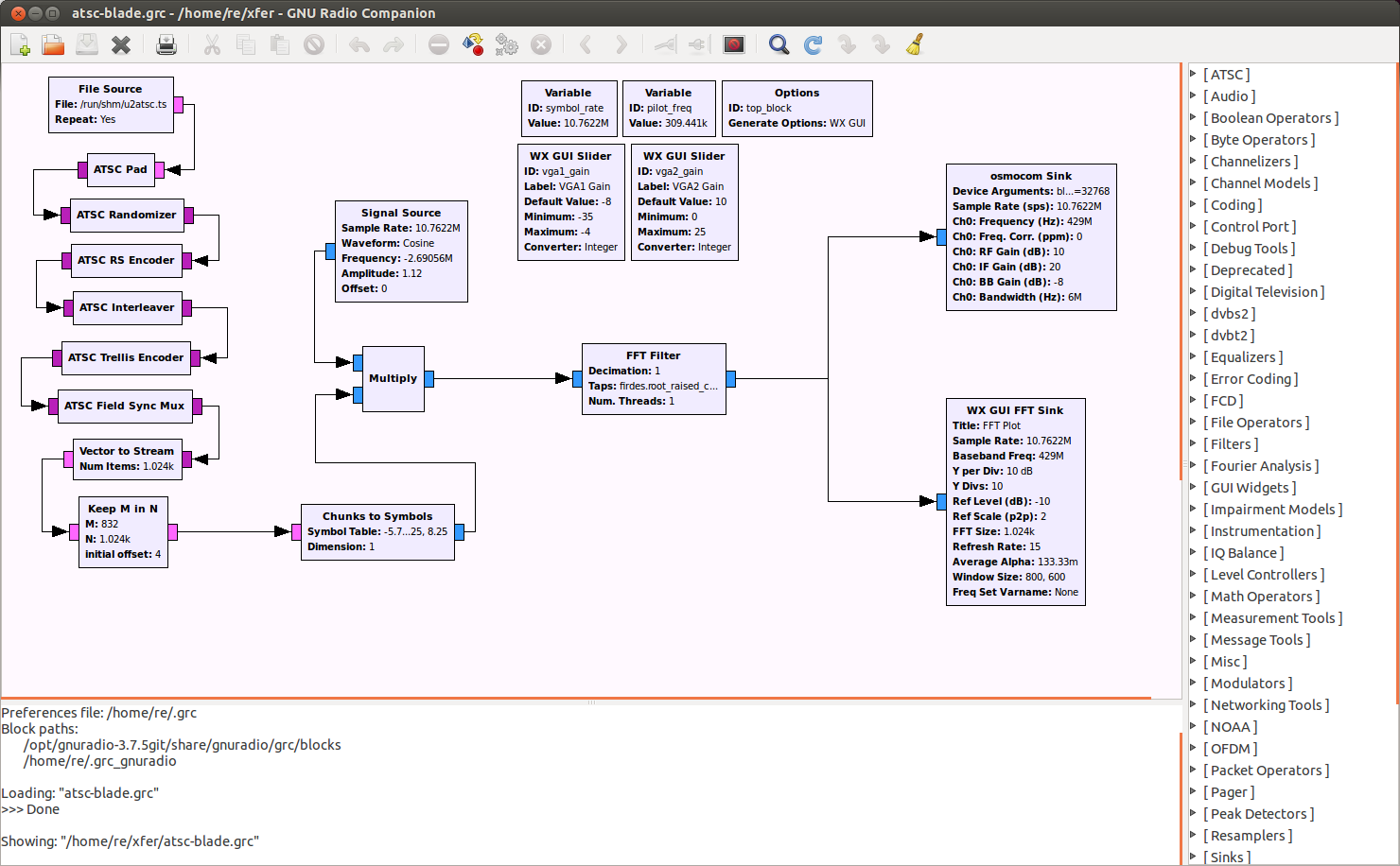

For those wishing to use the ATSC transmitter with gnuradio-companion, there's a set of block definitions available. Just copy the files to your GnuRadio blocks directory. On my system:

/opt/gnuradio-3.7.5git/share/gnuradio/grc/blocks

Adjust accordingly for your installation.

https://github.com/hpux735/grc_blocks

And a flow graph here.

https://github.com/hpux735/sdr-examples ... -blade.grc

Ron

/opt/gnuradio-3.7.5git/share/gnuradio/grc/blocks

Adjust accordingly for your installation.

https://github.com/hpux735/grc_blocks

And a flow graph here.

https://github.com/hpux735/sdr-examples ... -blade.grc

Ron

-

drmpeg

- Posts: 62

- Joined: Fri Mar 01, 2013 3:58 am

- Location: Silicon Valley

- Contact:

Re: ATSC Transmitter

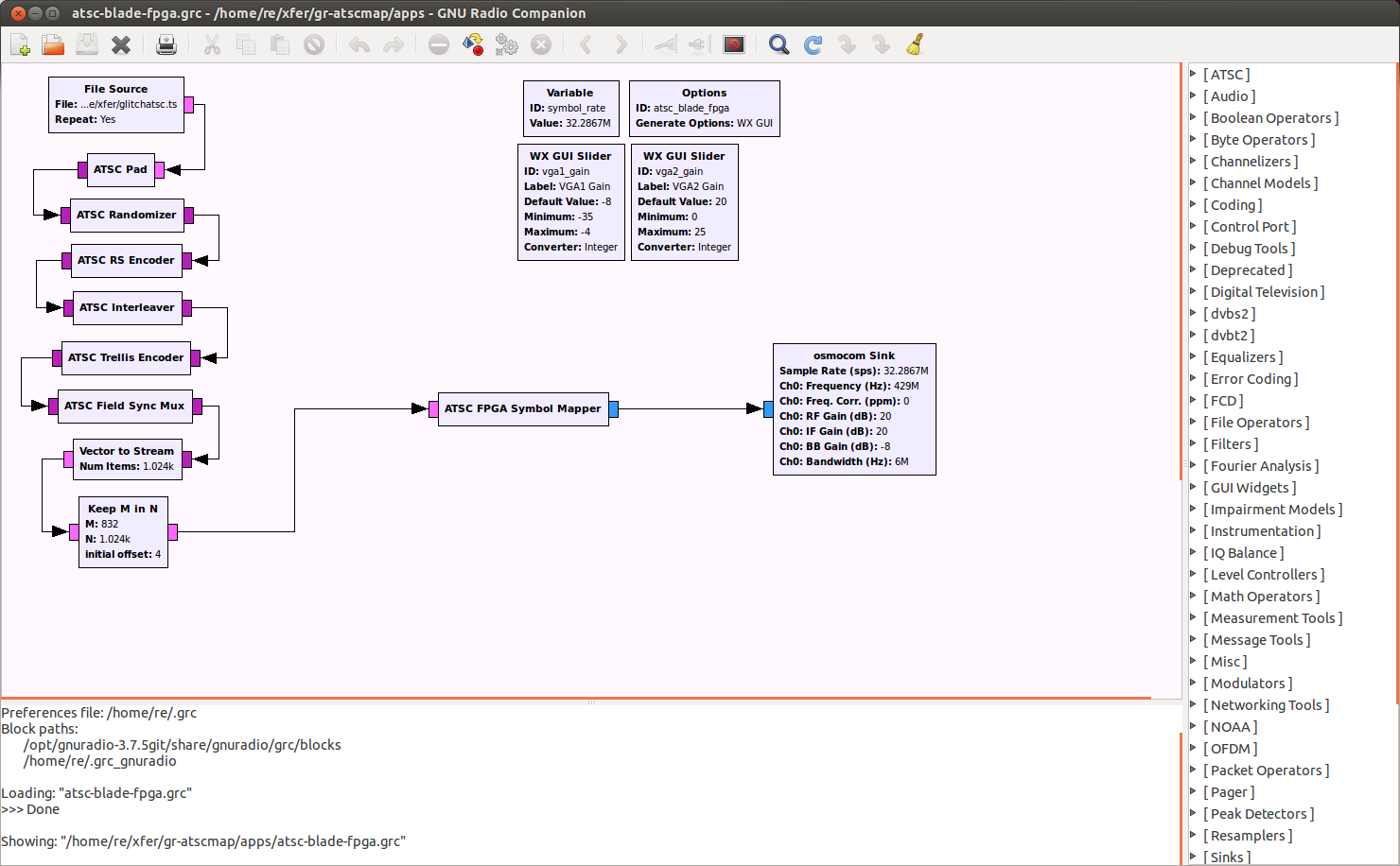

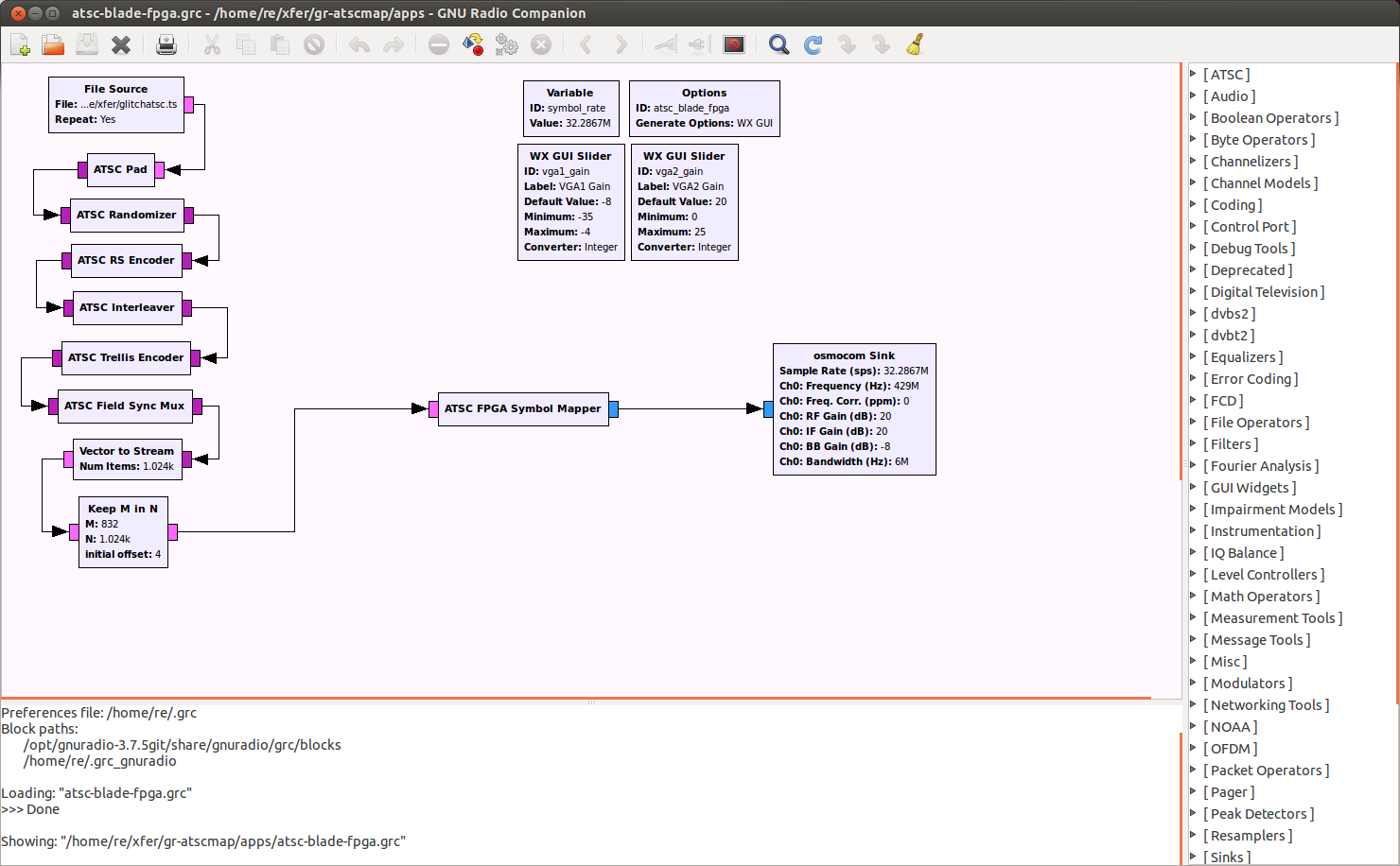

I've created a custom GnuRadio block for the new ATSC FPGA. It maps the 3-bit ATSC symbols to a floating point (gr_complex) stream that can be sent to the standard osmocom sink block.

https://github.com/drmpeg/gr-atscmap

The stand alone Python script is here:

https://github.com/drmpeg/gr-atscmap/bl ... de-fpga.py

ATSC FPGA images are here:

http://hoopycat.com/bladerf_builds/35e5 ... txx115.rbf

http://hoopycat.com/bladerf_builds/35e5 ... _txx40.rbf

A gnuradio-companion flowgraph is also available.

https://github.com/drmpeg/gr-atscmap/bl ... e-fpga.grc

Ron

https://github.com/drmpeg/gr-atscmap

The stand alone Python script is here:

https://github.com/drmpeg/gr-atscmap/bl ... de-fpga.py

ATSC FPGA images are here:

http://hoopycat.com/bladerf_builds/35e5 ... txx115.rbf

http://hoopycat.com/bladerf_builds/35e5 ... _txx40.rbf

A gnuradio-companion flowgraph is also available.

https://github.com/drmpeg/gr-atscmap/bl ... e-fpga.grc

Ron

-

hackair

- Posts: 1

- Joined: Mon Apr 20, 2015 10:46 am

Re: ATSC Transmitter

Hi drmpeg !

How do I create a ATSC receiver in gnu radio companion ? I haven't been able to find it on the internet. Clayton's tutorial was for transmission only, and I would love to learn how the receiver is made. But like all receivers, it is very complex to create. Could you help me out ?

- Sam

How do I create a ATSC receiver in gnu radio companion ? I haven't been able to find it on the internet. Clayton's tutorial was for transmission only, and I would love to learn how the receiver is made. But like all receivers, it is very complex to create. Could you help me out ?

- Sam

-

tara

- Posts: 7

- Joined: Tue Mar 26, 2019 1:37 am

- Contact:

Re: ATSC Transmitter

On the off chance that you expel the RRC channel (I know you're not transmitting over the air, so the test ought to be alright) how much lower does the CPU load get?

Is most by far of CPU time spent doing the RRC sifting?

With a 100 tap channel, symmetric, and 4 timekeepers for every image should transform into something like 26 multipliers to do the entire separating in the FPGA - presumably less since a portion of those taps are most likely going to be exceptionally little, or less difficult moves and includes.

I'd be interested the amount CPU it takes to do the interleaving, and RS encoding, versus simply the image forming a channel.

Is most by far of CPU time spent doing the RRC sifting?

With a 100 tap channel, symmetric, and 4 timekeepers for every image should transform into something like 26 multipliers to do the entire separating in the FPGA - presumably less since a portion of those taps are most likely going to be exceptionally little, or less difficult moves and includes.

I'd be interested the amount CPU it takes to do the interleaving, and RS encoding, versus simply the image forming a channel.

Electrical engineering